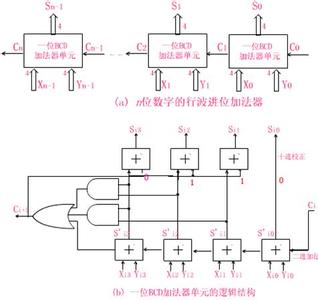

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。在电子学中,加法器是一种数位电路,其可进行数字的加法计算。在现代的电脑中,加法器存在于算术逻辑单元(ALU)之中。 加法器可以用来表示各种数值,如:BCD、加三码,主要的加法器是以二进制作运算。由于负数可用二的补数来表示,所以加减器也就不那么必要。

加法器_加法器 -基本方法

可以看出,上法是将32位的加法1位1位串行进行的,要缩短进行的时间,就应设法使上叙进行过程并行化。

加法器

逐位进位加法器,在每一位的计算时,都在等待前一位的进位。那么不妨预先考虑进位输入的所有可能,对于二进制加法来说,就是0与1两种可能,并提前计算出若干位针对这两种可能性的结果。等到前一位的进位来到时,可以通过一个双路开关选出输出结果。这就是进位选择加法器的思想。

提前计算多少位的数据为宜?同为32位的情况:线形进位选择加法器,方法是分N级,每级计算32/N位;平方根进位选择加法器,考虑到使两个路径(1,提前计算出若干位针对这两种可能性的结果的路径,2,上一位的进位通过前面的结构的路径)的延时达到相等或是近似。方法,或是2345666即第一级相加2位,第二级3位,第三级4位,第四级5位,第五级6位,第六级6位,第七级6位;或是345677即第一级相加3位,第二级4位,第三级5位,第四级6位,第五级7位,第六级7位。

进一步分析加法进行的机制,可以使加法器的结构进一步并行化。

令G = AB,P = A

爱华网

爱华网