三态缓冲器(Three-state-buffer),又称为三态门、三态驱动器,其三态输出受到使能输出端的控制,当使能输出有效时,器件实现正常逻辑状态输出(逻辑0、逻辑1),当使能输入无效时,输出处于高阻状态,即等效于与所连的电路断开。

三态缓冲器

三态缓冲器(Three-state-buffer),又称为三态门、三态驱动器,其三态输出受到使能输出端的控制,当使能输出有效时,器件实现正常逻辑状态输出(逻辑0、逻辑1),当使能输入无效时,输出处于高阻状态,即等效于与所连的电路断开。

缓冲器是数字元件的其中一种,它对输入值不执行任何运算,其输出值和输入值一样,但它在计算机的设计中有着重要作用。

缓冲器分为两种,常用缓冲器(常规缓冲器)和三态缓冲器。常规缓冲器总是将值直接输出,用在推进电流到高一级的电路系统。三态缓冲器除了常规缓冲器的功能外,还有一个选项卡通输入端,用E表示。当E=0和E=1时有不同的输出值。

缓冲器又可以分为输入缓冲器和输出缓冲器两种。前者的作用是将外设送来的数据暂时存放,以便处理器将它取走;后者的作用是用来暂时存放处理器送往外设的数据。有了数控缓冲器,就可以使高速工作的CPU与慢速工作的外设起协调和缓冲作用,实现数据传送的同步。由于缓冲器接在数据总线上,故必须具有三态输出功能。

当E=1时,选通,其输入直接送到输出;

若E=0,缓冲器被阻止,无论输入什么值,输出的总是高阻态,用Z表示。高阻态能使电流降到足够低,以致于类似缓冲器的输出没有与任何东东相连。

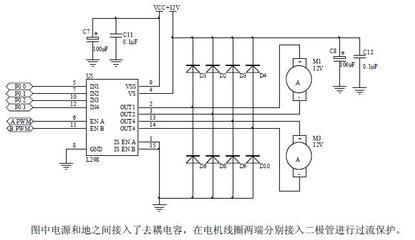

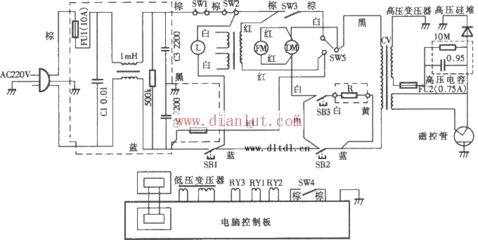

原理图

EDA代码

library ieee;

use IEEE.STD_LOGIC_1164.all;

ENTITY BUF3S IS

PORT (INPUT:IN STD_LOGIC_VECTOR;

ENABLE:IN STD_LOGIC;

OUTPUT:OUT STD_LOGIC_VECTOR);

END BUF3S;

ARCHITECTURE BHV OF BUF3S IS

BEGIN

PROCESS(ENABLE,INPUT)

IF ENABLE='1'THEN OUTPUT<=INPUT;

ELSE OUTPUT<="Z"

END IF;

END PROCESS;

END BHV;

爱华网

爱华网