SSL加速卡是计算机内的一种协议,用于安全保障。

ssl加速_SSL加速卡 -导言

网络信息安全已经成为电子商务和网络信息业发展的一个瓶颈,安全套接层(SSL)协议能较好地解决安全处理问题,而SSL加速器有效地提高了网络安全处理的性能。第一代和第二代SSL加速器提高了安全处理性能,但却不能满足系统扩展要求,即将推出的第三代SSL加速器集成度将更高,并采用新一代总线技术实现更高的安全处理性能。

那么怎样才能提供最好的安全性呢?利用安全套接层(SSL)协议是个较好的解决方法。

由Netscape开发的SSL已在网络业得到广泛的应用,它极大地促进了安全电子商务的发展,使各个公司能安全地开展基于网络的业务。但是,随着网络设备速度的加快需要大量计算,而速度缓慢的SSL正日益显示出不足之处,它无法以线速度(wire rate)进行安全性处理,而线速度正是当今系统设计工程师所追求的目标。

为了应对这种挑战,通信设计工程师们已开发出加速器来加快SSL处理。但是这些解决方案仍然不能满足当今互联网络设备的要求。

对于大多数通信业务来说,在系统设计中嵌入SSL技术,采用协议加速器而不是仅仅采用密码加速器IC方案才是这个问题的解决方法。在这种想法的推动下,提出了第二代SSL加速器与新的SSL加速技术,下面将详细讨论并分析这些方案对今后系统设计流程的影响。

ssl加速_SSL加速卡 -SSL浅析

SSL是一种会话层协议,位于TCP与应用层协议之间。它主要分成两个复杂阶段--握手(handshake)与记录层处理(record layer processing)。

SSL握手过程允许客户机与服务器系统之间协商修改协议、服务器识别和共享用于产生数据加密与认证用途的密钥的保密数据。

握手阶段也需要不少功能支持,如安全随机数的产生、RSA解密,以及采用一系列散列函数产生主秘(master secret)与密钥数据。记录层将字节数据流处理成记录块,并采用密码套件(cipher suite,一对加密与散列算法)对其进行加密与认证。在记录层阶段采用对称密码对用户数据加密,并采用某种散列算法对数据进行认证, 该算法是基于握手阶段产生的密钥。

然而SSL性能最大的问题来自产生SSL握手的RSA不对称密码函数。握手协议所要求的计算量非常巨大,可能会消耗系统的所有CPU资源,极大地降低系统数据吞吐量。

为了解决这个问题,设计工程师们开发出第一代SSL加速器。这些加速器试图将SSL握手部分的负载RSA解密移出网络服务器,让控制处理器来处理余下的握手函数(用于密钥创建的散列函数)以及记录层处理函数(大量的加密与认证)。

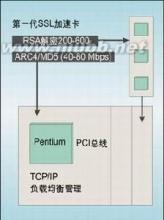

一个典型的第一代SSL加速器包含一个带很多SSL加速芯片的PCI板,每秒最多能处理200个解密算法,这比最初的SSL产品(不带加速器)快30到40倍。

ssl加速_SSL加速卡 -第一代SSL加速器

第一代SSL加速器每秒能处理600个RSA解密算法(图1)。在全速运行条件下,一个每秒运行600个RSA解密算法的系统需要约85Mbps的加密处理能力,对于RC4/MD5密码套件而言,其负载将占1GHz奔腾III CPU处理能力16%,而3DES/SHA-1密码套件则需要144%的CPU处理能力。

当RSA解密功能由SSL加速器实现后,CPU就不会过载,并有足够能力进行TCP/IP处理与记录层处理。当两个SSL功能单元之间建立平衡后,网络服务器就能高速发送加密的业务数据,虽然不能接近线速度,但远远好于不采用SSL加速器的性能。但是,可扩展性是第一代加速器所不能实现的性能。

为了在系统架构中增加更多的SSL加速器,设计工程师必须增加更多的服务器卡。对于设计工程师与运营商来说,显然是件很困难的事。由于每块卡的价格要几千美元,再加上上万美元的额外服务器费用,使得这种解决方案的成本迅速攀升。

从性能角度看,由于CPU仍要从事大量的加密工作,加速卡数量的增加所提高的效率非常有限。CPU既要执行越来越多的TCP/IP处理,同时又要负责加密计算,因此第一代系统的可扩展性极其有限。

由于上述问题的存在,设计工程师只好又重新寻求新的加速技术,最后他们用单个芯片开发出完整的SSL加速产品。

ssl加速_SSL加速卡 -第二代加速器

虽然第一代产品通过SSL加速器处理RSA解密功能来提高性能,但系统级的总体性能仍不理想,而采用IC形式推出的第二代产品能增加每秒握手次数。

第二代SSL加速器设计工程师很快发现需要在握手与加密计算的吞吐量(异步与同步操作)之间取得均衡,一味地提高每秒内的握手次数只会产生新的瓶颈。随着密码套件处理量的增加,CPU资源很快就会耗尽,也削弱了对TCP/IP的处理能力。

例如,即使主处理器采用1GHz奔腾III处理器,一个每秒能发送2,000次RSA握手的纯RSA解密器也会给主处理器带来沉重的负载。对于RC4-MD5密码套件来说这些负载将消耗55%的CPU资源,而对于需要大量计算的3DES-SHA1密码套件来说可能需要近500%的CPU资源。

迅速增加握手次数将使瓶颈后移到CPU,这时,只要记录层存在大量加密处理就将产生系统阻塞。

为了避免这种瓶颈问题,芯片与系统设计工程师开始寻求用IC来实现SSL加速。这些通常被称为网络安全处理器的IC会卸载主处理器的握手函数(RSA解密与密钥生成)以及记录层的大量加密与认证函数,使CPU能腾出更多的资源来执行包处理,从而提升系统总体性能。

采用SSL加速器IC的优势在于能分担主机上的SSL协议处理,以及提供更多RSA解密的能力。为了使这些IC能充分发挥系统级性能,所有SSL组件必须协同工作。为了给完整的SSL协议提供服务,安全处理器芯片上需要集成多个公用组件,包括随机数发生器、公钥加密模块和密码加密/认证模块。

除了服务整个SSL协议外,网络安全处理器IC必须能快速处理数据的输入输出。为了实现这个目的,这些处理器必须优先采用66MHz/64位 PCI总线。为了加快数据的输入输出速度,随机数发生器、公钥引擎与密码加密/认证模块一般应链接在同一PCI总线上,这样在系统设计中能方便地将它们链接到其它PCI架构。

为了进一步方便集成,制造商还需将安全处理器置于PCI板上。因此,制造商需要解决一般OEM厂商都会遇到的I/O困难,尤其在将这些IC置入PCI系统架构的时候。

ssl加速_SSL加速卡 -加速器的实现

实现第二代SSL加速器IC的一个关键问题是在系统架构的何处实现。事实上,这些器件可以在网络的SSL设备、第4层/第7层交换机和网络服务器中实现。

在目前典型的IP网络结构中,业务是通过L4/L7智能负载均衡交换机进入数据中心。输入的网络客户机请求将被分配到后端的若干网络服务器或网络缓冲器中。L7应用数据在送入网络服务器之前要做一定的解析。由于SSL要加密L4以上的所有数据,在数据被完全解密前无法执行对应用层数据的智能内容交换。

在目前的架构中,SSL加速功能很可能以单个PCI插卡的形式配置于SSL设备和网络服务器中。交换机将SSL业务直接转移到该设备中并在那里执行解密,然后设备将未加密的业务数据送回到交换机,这些数据与解密的应用数据进行负载均衡。

紧密集成的下一步是将SSL加速器直接集成到L4/L7交换机中。要做到这一点,网络安全处理器可以附加在代理卡上(而不是一块简单的PCI板),在代理卡上还应安装运行SSL代理程序的控制处理器。这种设备基本上能代替加速设备,可直接集到进交换机端口。

网络安全处理器也可直接配置在网络服务器中。这种方式对较小型的企业特别有效,因为这些企业通常不会配备大型的服务器阵列和网络交换机。

在当前架构中,SSL加速功能很可能以单个SSL插卡的形式配置在网络服务器中。从发展的角度看,某些情况下的SSL加速器配置可以移植到用户卡,因为加速系统会更直接地集成到总体系统设计中。

ssl加速_SSL加速卡 -本文小结

目前,设计工程师们正在努力开发第三代SSL加速器。这种能提供真正千兆位加密数据流的第三代加速器有望在今年夏季面市。为了实现这一目标,一个均衡系统每秒将至少发送一万次RSA握手,这个目标已经成为加密型全双工千兆位以太网的非正式标准。要达到如此高的性能,需要在第二代芯片的基础上对结构作出重大修改。

为了满足千兆位传输速率的基本性能要求,第三代加速器需要将随机数发生器、公钥引擎和加密/认证模块集成在同一芯片上。这些功能模块需要采用高速专用处理内核用于并行运行的密钥加密原语(AES、MD5、SHA-1、3DES和ARC-4),并采用新一代总线技术,如PCI-X、HyperTransport或3GIO。

爱华网

爱华网