FPGA寄存器的上电初值

FPGA内部寄存器的上电初值是什么? 有说是低的,有说是高的,也有说和器件相关的,还有些人说是不确定. 对于一个系统来讲, 用户并不在意初值是高电平,或者是低电平,用户真正关心的是寄存器的初值是不是确定可预测的,也就是说每次编译,每次上电的初值是不是一致的。

来举个例子,有个客户在调试FPGA设计,在头一个月编译的几百次结果中,一个寄存器的初值一直都是低电平。某一天改了一部分看似不相关的代码之后,这个寄存器的初值从此之后就变成高电平了。这种情况通常会让用户不知所措,非常痛苦。后来在我们的一起努力下,采用了一些措施,最终可以控制寄存器的初值.

那么到底是什么?简单说,寄存器的初值是由综合工具(synthesistool)决定下来的,综合synthesis过后,电路网表就确定了,初值也就决定了。换句话说,初值不会随后端的布局布线过程影响。但是如果没有针对性的规则来约束综合synthesis,那么一次编译后的初值和上一次编译的初值是有可能不一样的,当然更多的时候是一样的。本文后面会对这个现象作进一步分析的.

1. 工作原理

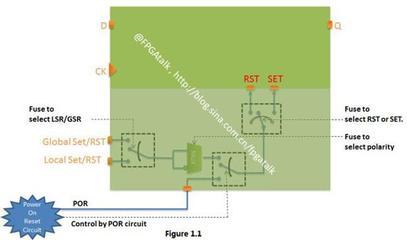

寄存器的初值到底是怎么回事? 我们来看一张图。Figure1.1是FPGA内部一个寄存器的复位功能模型。FPGA的寄存器要么工作在复位RST模式,要么工作在置位SET模式,不会同时支持RST和SET功能。这是当前市场是多数FPGA的共同特性。RST或者SET的选择是通过下载到FPGA的Fusebit决定的。FPGA芯片内部有一个上电检测模块,一旦检测到电源电压超过检测门限后,就产生一个上电复位脉冲(Power OnReset)送给所有的寄存器. 对于某个特定的寄存器,POR的作用是RST还是SET, 完全取决于编程到FPGA的FUSEbit。而FUSE值在综合(synthesis)之后,事实上已经完全确定了.

- FPGA的寄存器只能配置为RST或者SET两种模式之一,而不能同时支持RST和SET。

- RST或者SET信号的极性是可编程的。

- 每一个寄存器都可以配置为受全局复位(GSR)控制,或者局部复位(LSR)控制。

- FPGA有一个上电检测电路,上电检测电路产生上电复位POR,POR的作用取决于FUSE的配置。除了上电,重新加载FPGA也会产生POR。

2.代码风格和初值的关系

下面我们来看几个例子,看不同的代码和初值的对应关系。

2.1带有异步复位的寄存器代码

module top(

input wire rst,

input wire clk,

input wire d,

input wire cke,

output reg q

);

always @(posedge rst or posedgeclk)

begin

if(rst==1'b1)

q<= 1'b0;

elseif(cke==1'b1)

q<=d;

end

endmodule

这种带有异步复位的寄存器描述,其对应的网表如图Figure 2.1. 显然上电初值为0.

2.2 带有异步置位的寄存器代码

module top(

input wire rst,

input wire clk,

input wire d,

input wire cke,

output reg q

);

always @(posedge rst or posedgeclk)

begin

if(rst==1'b1)

q<= 1'b1;

elseif(cke==1'b1)

q<=d;

end

endmodule

这种带有异步置位的寄存器描述,其对应的网表如图Figure 2.2. 显然上电初值为1.

2.2没有异步复位,也没有异步置位的寄存器代码

这种情况比较复杂,让我们来看两个例子。

2.2.1 较简单的场景

module top(

input wire clk,

input wire d,

input wire cke,

output reg q

);

always @(posedgeclk)

begin

if(cke==1'b1)

q<=d;

end

endmodule

在寄存器的输入比较简单的情况下,其对应的网表如图Figure 2.3. 综合工具不使用RST/SET功能。FPGA后端工具默认使用RST,并把RST连接到地GND. 那么显然上电初值为0.

2.2.2 较复杂的场景

.....

.....

always @(posedgeclk)

begin

if(cond1[7:0] == 8'h55)

q <=1’b0;

else if(cond2[7:0] == 8'haa)

q <= 1’b1;

else if(cond3[7:0] == 8'h0f)

q <= 1’b0;

else if(cond4[7:0] ==8'h00)

q <= 1’b1;

else;

end

.....

.....

在寄存器的输入相对复杂的情况下, 综合工具有很大的空间去做优化.一种可能的优化结果是, 在不改变逻辑功能的前提下,综合工具为了降低数据输入端D的逻辑复杂度,抽取一个节点信号或作RST,或作SET.

例如,综合工具可以随机的输出下面三种结果中的一个,虽然他们的逻辑功能都是一样的,但是初值就完全不同.这样就会出现两次编译的初值不一致的情况.

Case 1.把部分信号打包到RST端,寄存器初值为0

Q . D = f1( cond2, cond3,cond4,f2);

Q . RST = f2(cond1,f1);

Case 2.把部分信号打包到SET端,寄存器初值为1

Q . D = f3(cond1, cond3,cond4, f4);

Q . SET = f4(cond2,f3);

Case 3.不用RST/SET,寄存器初值为0

Q . D = f5(cond1, cond2, cond3,cond4);

Q . RST = GND ;

那么,怎么办?

办法 1 : 对于这种情况,把代码风格改一改,使用下面的代码风格,可以让每次编译都有一致的初值0. 用两个process来描述寄存器,第一个纯组合,第二个纯时序,并使用综合约束syn_keep(以Synplify为例)来保留组合逻辑节点.

...

reg q_buf;

always@(*)

begin

if(cond1[7:0] == 8'h55)

q_buf <=1’b0;

else if(cond2[7:0] == 8'haa)

q_buf <= 1’b1;

else if(cond3[7:0] == 8'h0f)

q_buf <= 1’b0;

else if(cond4[7:0] ==8'h00)

q_buf <= 1’b1;

else;

end

always @(posedge clk)begin

q <= q_buf ;

end

.....

办法 2 :对于这种情况,有些综合工具支持上电初值预设,具体可以查看帮助.

办法 3 :代码中定义寄存器的同时赋初值,如:

reg [3:0] myreg = 4’b0101 ;

这其实是仿真语法,本来不能用于综合synthesis的. 但有些综合工具的某些版可以识别为初值, 但是不能够确保一定被识别.不建议使用.

小结

可见, 寄存器初值是由综合工具决定的,用户可以通过适当的代码风格,或者综合选项等设置寄存器初值. 如果对于寄存器的初值不作约束, 综合工具可以有更大的优化空间,降低逻辑级数.

爱华网

爱华网