--2.5分频

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity xiaoshufenpinis

port(clk:in std_logic;

dout:out std_logic);

end entity;

architecture x ofxiaoshufenpin is

signal p,q:std_logic_vector(2 downto 0);

begin

process(clk)

begin

if (clk'eventand clk='1') then

ifp="100" then --4

p<="000";

elsep<=p+1;

endif;

endif;

end process;

process(clk)

begin

if (clk'event and clk='0')then

if q="100"then --4

q<="000";

elseq<=q+1;

endif;

endif;

end process;

dout<='1' when p="000" or q="010"--2

else'0';

end x;

--3.5分频(N.5分频)

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity xiaoshufenpinis

port(clk:in std_logic;

dout:out std_logic);

end entity;

architecture x ofxiaoshufenpin is

signal p,q:std_logic_vector(2 downto 0);

begin

process(clk)

begin

if (clk'eventand clk='1') then

ifp="110" then --6(或2N)

p<="000";

elsep<=p+1;

endif;

endif;

end process;

process(clk)

begin

if (clk'event and clk='0')then

if q="110"then -6(或2N)

q<="000";

elseq<=q+1;

endif;

endif;

end process;

dout<='1' when p="000" or q="011"--0或3(或N/2)

else'0';

end x;

半整数分频的另外一种实现方法:要实现分频系数为2.5的分频器,可采用以下方法:设计一个模为3的计数器,再设计一个脉冲扣除电路,加在模3计数器输出之后,每来两个脉冲就扣除一个脉冲,就可以得到分频系数为2.5的小数分频器。采用类似方法,可以设计分频系数为任意半整数的分频器。

小数分频的基本原理是:采用脉冲吞吐计数,设计两个不同分频比的整数分频器,通过控制单位时间内两种分频比出现的次数,从而获得所需的小数分频值。例如,设计一个分频系数为10.1的分频器,可以将分频器设计成9次10分频,1次11分频,这样总的分频值为

9×10+1×11)/(9+1)=10.1

从这种实现方法的特点可以看出,由于分频器的分频值在不断改变,因此分频后得到的信号抖动大。

当分频系数为N-0.5(N为整数)时,可控制扣除脉冲的时间,使输出为一个稳定的脉冲频率,而不是一次N分频,一次N-1分频。

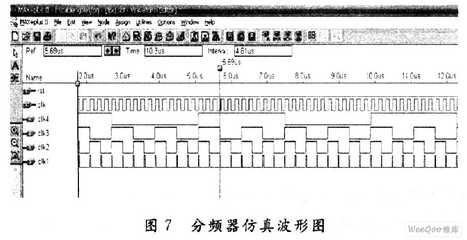

设需要设计一个分频系数为N-0.5的分频器,其电路可由一个模N计数器、二分频器和一个异或门组成,如图1所示

图1:小数分频原理图

在实现时,模N计数器可设计成带预置的计数器,这样就可以实现任意分频系数为N-0.5的分频器。

--2.5分频

library ieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

useieee.std_logic_arith.all;

entityxiaoshufenpin is

port

(clk:instd_logic;

qout1:buffer std_logic;

qout2:buffer std_logic;

clkout:out std_logic

);

endxiaoshufenpin;

architecturebehave of xiaoshufenpin is

constantcounter_len:integer:=3;--模参数设置

signal clk_tem:std_logic;

begin

qout1<=clk xorqout2;--异或

process(qout1)--模为3的计数器

variablecnt:integer range 0 tocounter_len-1;

begin

ifqout1'event and qout1='1'then

ifcnt=counter_len-1then

cnt:=0;

clk_tem<='1';

clkout<='1';

else

cnt:=cnt+1;

clk_tem<='0';

clkout<='0';

endif;

endif;

endprocess;

process(clk_tem)--二分频器

variabletem:std_logic;

begin

ifclk_tem'event and clk_tem='1'then

tem:=nottem;

endif;

qout2<=tem;

endprocess;

endbehave;

爱华网

爱华网