冯·诺依曼结构

传统计算机采用冯·诺依曼(Von Neumann)结构,也称普林斯顿结构,是一种将程序指令存储器和数据存储器并在一起的存储器结构。冯·诺依曼结构的计算机其程序和数据公用一个存储空间,程序指令存储地址和数据存储地址指向同一个存储器的不同物理位置;采用单一的地址及数据总线,程序指令和数据的宽度相同。处理器执行指令时,先从储存器中取出指令解码,再取操作数执行运算,即使单条指令也要耗费几个甚至几十个周期,在高速运算时,在传输通道上会出现瓶颈效应。

如图 1-3所示,冯·诺依曼结构的计算机由CPU和存储器构成,程序计算器(PC)是CPU内部指示指令和数据的存储位置的寄存器。CPU通过程序计数器提供的地址信息,对存储器进行寻址,找到所需要的指令或数据,然后对指令进行译码,最后执行指令规定的操作。

在这种体系结构中,程序计数器只负责提供程序执行所需要的指令和数据,而不决定程序流程。要控制程序流程,则必须修改指令。

目前使用冯·诺依曼结构的CPU和微控制器有很多。其中包括英特尔公司的808--6及其他CPU,ARM公司的ARM7、MIPS公司的MIPS处理器也采用了冯·诺依曼结构。

哈佛结构

哈佛(Harvard)结构是一种将程序指令存储和数据存储分开的存储器结构。哈佛结构是一种并行体系结构,它的主要特点是将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个相互独立的存储器,每个存储器独立编址、独立访问。与两个存储器相对应的是系统中的4套总线:程序的数据总线与地址总线,数据的数据总线与地址总线。这种分离的程序总线和数据总线可允许在一个机器周期内同时获取指令字(来自程序存储器)和操作数(来自数据存储器),从而提高了执行速度,是数据的吞吐率提高了1倍。又由于程序和数据存储器在两个分开的物理空间中,因此取指和执行能完全重叠。

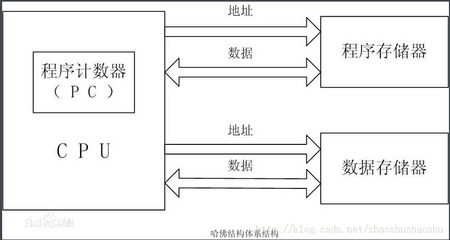

如图1-4所示,哈佛结构的计算机由CPU、程序存储器和数据存储器组成,程序存储器和数据存储器采用不同的总线,从而提供了较大的存储器带宽,使数据的移动和交换更加方便,尤其提供了较高的数字信号处理性能。

哈佛结构的CPU通常具有较高的执行效率。目前使用哈佛结构的CPU和微处理器有很多,除了所有的DSP处理器,还有摩托罗拉公司的MC68系列、Zilog公司的Z8系列、ATMEL公司的AVR系列和ARM公司的ARM9、ARM10和ARM11等。

爱华网

爱华网