FPGA加法器设计

杨剑 2011.11.29

加法作为一种基本运算,大量运用在数字信号处理和数字通信的各种算法中。由于加法器使用频繁,因此其速度往往影响着整个系统的运行速度。如果可以实现快速加法器的设计,则可以提高整个系统的处理速度。

加法运算是最基本的算数运算,在多数情况下,无论是乘法、除法还是减法以及FFT等运算,最终都可以分解为加法运算来实现,因此对加法运算的实现进行一些研究是非常必要的。实现加法运算有如下一些方法:

(1)级连加法器;

(2)并行加法器;

(3)超前进位加法器;

(4)流水线加法器。

1、级连加法器

级连加法器是由1位全加器级连构成的,本位的进位输出作为下一级的进位输入。级连加法器的结构简单,但N位级连加法运算的延时是1为全加器的N倍,延时主要是由于进位信号级连造成的。在需要高性能的设计中,这种结构不宜采用。

module add_jl(sum,cout,a,b,cin);

output [3:0] sum;

output cout;

input [3:0] ina,inb;

input cin;

wire [3:1] c;

full_add1 f0 (ina[0],inb[0],cin,sum[0],c[1]);//级连描述

full_add1 f1 (ina[1],inb[1],c[1],sum[1],c[2]);

full_add1 f2 (ina[2],inb[2],c[2],sum[2],c[3]);

full_add1 f3 (ina[3],inb[3],c[3],sum[3],cout);

modulefull_add1(ina,inb,cin,sum,cout);//1位全加器

input ina,inb,cin;

output sum,cout;

wire s1,m1,m2,m3;

and (m1,ina,inb),

(m2,inb,cin),

(m3,ina,cin);

xor (s1,a,b),

(sum,s1,cin);

or (cout,m1,m2,m3);

endmodule

2、并行加法器

并行加法器可采用Verilog语言的加法运算符直接描述,或称为数据流描述方式,实现容易,其运算速度快,但耗费资源多,尤其是当加法运算的位数较宽时,其耗用资源将会大大增加。

module add_bx(cout,sum,a,b,cin);

output [7:0] sum;

output cout;

input [3:0] a,b;

input cin;

assign {cout,sum}=a+b+cin;

endmodule

3、超前进位加法器

级连加法器的延时主要是由于进位的延时造成的,因此要加快加法器的运算速度,就必须减小进位延迟,超前进位链能有效地减少进位的延迟。

这里以4位超前进位链的推导为例介绍超前进位的概率。

首先对于1位全加器,其本位值与进位输出可表示如下:

sum=a⊕b⊕cin

cout=(a·b)+(a·cin)+(b·cin)=ab+(a+b)cin

从上面式子可以看出:如果a和b都为1,则进位输出为1;如a和b有一个为1,则进位输出等cin.

另G=ab,P=a+b,则有:

cout=ab+(a+b)cin=G+P·cin

由此可以得出用G和P来写出4位超前进位链如下(设定4位被加数和加数位A和B,进位输入为Cin,进位输出为Cout,进位产生Gi=AiBi,进位传输Pi=Ai+Bi):

C0=Cin

C1=G0+P0C0=G0+P0Cin

C2=G1+P1C1=G1+P1(G0+P0Cin)=G1+P1G0+P1P0Cin

C3=G2+P2C2=G2+P2(G1+P1C1)=G2+P2G1+P2P1G0+P2P1P0Cin

C4=G3+P3C3=G3+P3(G2+P2C2)=G3+P3G2+P3P2G1+P3P2P1G0+P3P2P1P0Cin

Cout=C4

由上面的超前进位链可以看出:各个进位彼此独立产生,将进位级连传播给去掉了,因此,减少了进位产生的延迟时间。

同样,可推导出下面的式子:

sum=A⊕B⊕Cin=(AB)⊕(A+B)⊕Cin=G⊕P⊕Cin

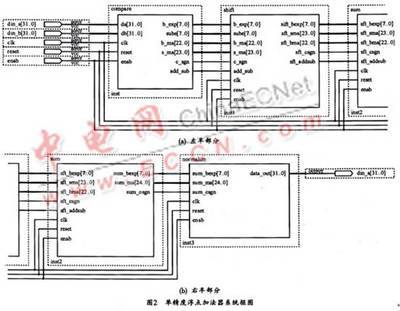

4、流水线加法器

以上实现的加法器虽然尽量减少了延时,但还是不可避免地有多级门延时和布线延时,随着位数的增加,延迟还会增加。为了设计更快的加法器,可以采用流水线设计技术(Pipeline),以提高系统的运行频率。其基本设计思想是在逻辑电路中插入若干寄存器来暂存中间结果,虽然多了一些寄存器资源,但减少了每一级组合的延时,因为可以提高整个加法器的运行频率,是用于提高所设计系统运行速度的一种有效方法。

流水线操作的概念以下图来说明,在图中,假设某个复杂逻辑功能的实现需要较长时间,我们可以将其分解为几个步聚来实现,每一步延时变为原来的1/3,并在各步之间加入寄 存器,以暂存中间结果,这样的话,整个系统的最高工作频率得到很大的提高。

爱华网

爱华网