一、实验目的

1.熟悉QUARTUSII软件的使用;

2.熟悉实验箱的使用;

3.掌握利用层次结构描述法设计电路。

二、实验原理及说明

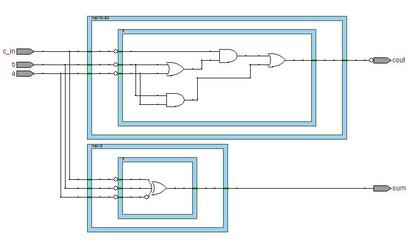

由数字电路知识可知,一位全加器可由两个一位半加器与一个或门构成,其原理图如图1所示。该设计利用层次结构描述法,首先设计半加器电路,将其打包为半加器模块;然后在顶层调用半加器模块组成全加器电路;最后将全加器电路编译下载到实验箱,其中a,b,cin信号可采用实验箱上键1、键2和键3进行输入,s,co信号采用D1与D2发光二极管来显示。

图1.1 全加器原理图

三、实验步骤

1.建立full_adder的工程(project)

在QUARTUSII软件下创建一工程,工程名为full_adder,芯片名为EP1C3T144,选择FPGA目标器件,根据DE2的平台情况,选择cycloneII系列的EP2C35F672C6,注意工程路径不要放到安装路径;

2.设计half_adder的VHDL模块

新建VHDL语言文件,输入如下半加器VHDL语言源程序,并存盘为half_adder.vhd;

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity half_adder is

port( a : in STD_LOGIC;

b : inSTD_LOGIC;

s : outSTD_LOGIC;

co: out STD_LOGIC );

end half_adder;

architecture half_adder of half_adder is

signal c,d:std_logic;

begin

c<=a or b;

d<=a nand b;

co<=not d;

s<=c and d;

end half_adder;

3.验证half_adder.vhd的正确与否,进行仿真

一般先进行功能仿真,再进行时序仿真。为了仿真,首先编辑测试文件。本次实验由于系统简单,采用对输入信号进行输入波形编辑的方法得到激励文件编辑波形文件并存盘

爱华网

爱华网