【摘 要】 以交通灯控制器设计为例, 系统地阐述了用VHDL实现数字电路的设计过程,展示了VHDL的强大功能和非凡特性。

关键词: 数字系统、交通灯控制器、EDA、 QuartusII、VHDL

【Abstract 】 Through analyzing the design processof TLC(Traffic Light Controller),this paper describes in detail thedesign process of implementing the digital circuit with VHDL,and itshows the powerful function and excellent character ofVHDL..

Keywords: digitalsystem、traffic light-control、EDA、 Quartus II、VHDL

一、引言

VHDL的英文全名是Very-High-Speed Integrated CircuitHardwareDescriptionLanguage,诞生于1982年。1987年底,VHDL被ieee和美国国防部确认为标准硬件描述语言。自IEEE公布了VHDL的标准版本,IEEE-1076(简称87版)之后,各EDA公司相继推出了自己的VHDL设计环境,或宣布自己的设计工具可以和VHDL接口。此后VHDL在电子设计领域得到了广泛的接受,并逐步取代了原有的非标准的硬件描述语言。现在,VHDL和Verilog作为IEEE的工业标准硬件描述语言,又得到众多EDA公司的支持,在电子工程领域,已成为事实上的通用硬件描述语言。有专家认为,在新的世纪中,VHDL与Verilog语言将承担起大部分的数字系统设计任务。

二、设计要求

1、显示甲乙通道的绿、黄、红的指示状态。

2、复位按键实现总体计数清零功能。

3、实现正常的倒计时功能. 用数码管作为倒计时显示,显示时间为绿灯26s,黄灯6s红灯30s。

三、设计原理

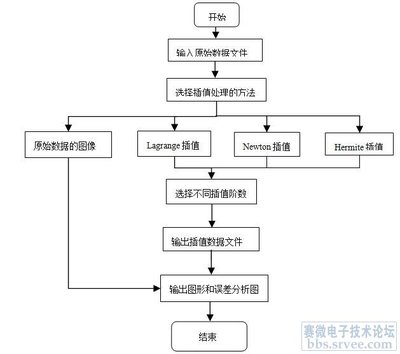

交通管理器控制十字路口甲乙两条道路的红黄绿三色灯,指挥车辆和行人安全通行,十字路口交通管理器示意图中R1,Y1,G1是甲道红黄绿灯;R2,Y2,G2是乙道红黄绿灯。

图1 十字路口交通管理器示意图

交通管理器由控制器和受控制器的三个定时器以及六个交通管理灯组成。三个定时器分别确定甲道和乙道通行时间t3,t1和公共停车时间t2。这三个定时器采用以秒信号为时钟的计数器来实现,c1,c2,c3分别是这些定时器的工作使能信号,即当c1,c2,或c3为1时,相应的定时器开始计数,w1,w2,w3是定时计数器的指示信号,计数器在计数过程中,相应的指示信号为0,计数结束时为1。

图2 交通器工作流程图

本设计采用层次描述方式,也采用原理图输入和文本输入混合方式建立描述文件,三个定时器的模分别为26,5,和30。

四、交通管理器的设计

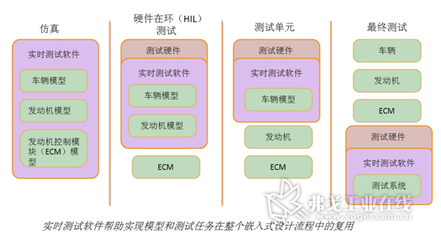

1、顶层原理图(如下图3)

图3 交通管理器顶层图形文件

在顶层图形文件中的各模块,其功能用第二层次VHDL源文件描述。

2、底层程序traffic_control --控制器逻辑描述

libraryieee;

useieee.std_logic_1164.all;

entitytraffic_control is

port(

clk:instd_logic;

c1,c2,c3:outstd_logic;--各定时计数器器的使能信号

w1,w2,w3:instd_logic;--各定时计数器器的工作信号

r1,r2:outstd_logic;--两个方向的红灯信号

y1,y2:outstd_logic;--两个方向的黄灯信号

g1,g2:outstd_logic;--两个方向的绿灯信号

reset:instd_logic);--复位信号

end traffic_control;

architecture behave of traffic_control is

type state_space is(s0,s1,s2,s3);

signal state:state_space;

begin

process(clk)

begin

if reset='1'then

state<=s0;

elsif(clk'event and clk='1')then

case state is

when s0=>ifw1='1'then

state<=s1;

end if;

when s1=>if w2='1'then

state<=s2;

end if;

when s2=>if w3='1'then

state<=s3;

end if;

when s3=>if w2='1'then

state<=s0;

end if;

end case;

end if;

end process;

c1<='1'when state=s0 else'0';

c2<='1'when state=s1 or state=s3else'0';

c3<='1'when state=s2 else'0';

r1<='1'when state=s1 or state=s0else'0';

y1<='1'when state=s3 else'0';

g1<='1'when state=s2 else'0';

r2<='1'when state=s2 or state=s3else'0';

y2<='1'whenstate=s1 else'0';

g2<='1'whenstate=s0 else'0';

end behave;

3、底层程序count30--30秒定时器源文件

library ieee;

use ieee.std_logic_1164.all;

entity count30 is

port(clk:in std_logic;

enable:in std_logic;

c:outstd_logic);

end count30;

architecture behave of count30is

begin

process(clk)

variable cnt: integer range 30 downto 0;

begin

if(clk'event and clk='1')then

if enable='1'and cnt<30 then

cnt:=cnt+1;

else

cnt:=0;

end if;

end if;

if cnt=30 then

c<='1';

else

c<='0';

end if;

end process;

end behave;

4、底层程序count26 --26秒定时器源文件

library ieee;

use ieee.std_logic_1164.all;

entity count26 is

port(clk:in std_logic;

enable:in std_logic;

c:out std_logic);

end count26;

architecture behave of count26 is

begin

process(clk)

variable cnt: integer range 26 downto 0;

begin

if(clk'event and clk='1')then

if enable='1'and cnt<26 then

cnt:=cnt+1;

else

cnt:=0;

end if;

end if;

if cnt=26 then

c<='1';

else

c<='0';

end if;

end process;

end behave;

5、底层程序count05--5秒定时器源文件

library ieee;

use ieee.std_logic_1164.all;

entity count05 is

port(clk:in std_logic;

enable:in std_logic;

c:out std_logic);

end count05;

architecture behave of count05 is

begin

process(clk)

variable cnt: integer range 5 downto 0;

begin

if(clk'event and clk='1')then

if enable='1'and cnt<5 then

cnt:=cnt+1;

else

cnt:=0;

end if;

end if;

if cnt=5 then

c<='1';

else

c<='0';

end if;

end process;

end behave;

使用方法是将四个底层程序count05,count26,count30和traffic_control打包成元件符号存盘用于顶层原理图设计;

编译器将顶层图形输入文件和第二层次功能块VHDL输入文件结合并编译,确定正确无误后,则可产生交通管理器的目标文件。

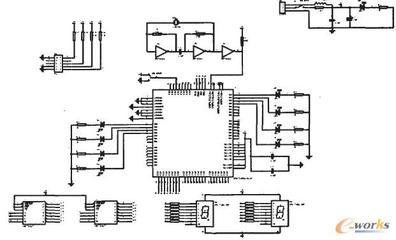

五、仿真结果

由下图看出,首先是甲道禁止(r1为高电平),乙道通行(g2为高电平);经过30秒后,转换为甲道禁止(r1为高电平),乙道停车(y2为高电平);经过5秒后,转换为甲道通行(g1为高电平),乙道禁止(r2为高电平);经过26秒后,转换为甲道停车(y1为高电平),乙道禁止(r2为高电平);再经过5秒后,进入开始时的状态,完成一个循环。从波形图中看出,完成了设计要求。

图4 交通管理器仿真波形

六、结论

编译成功后,我们基本完成我们的任务要求,特别是设计任务是有关生活实际的问题,“交通灯”大家每天都在接触,和所需配件。在电脑上进行仿真和编译,这个过程中老师给了很大的帮助,同学之间的讨论,能很快的了解和分析问题,特别是在编译出错时,同学组员之间互相帮助解决问题,学到了不少知识。从实验中才真正了解到它的工作原理,让我们在生活和身边运用并深刻体会了书本知识具体化。这次的实验中,我们更进一步体会到自主学习和团队合作的乐趣与必要性,我们所使用的VHDL语言,掌握了它的使用。在学习和制作过程中,老师的态度很明确,让学生自己去做,为了完成项目,我在网络上找到了许多相关资料,大大扩充自己的知识面,使许多以前想 解决却无法解决的困难迎刃而解。总结起来是受益良多。

七、参考文献

[1]宋正伟 .EDA技术及应用 . 清华大学出版社 . 2006.1

[2]潘松,黄继业 . EDA技术实用教程(第三版) . 科学出版社 . 2006.9

爱华网

爱华网