飞碟、磁能、反重力讲座

刘中凯2014年9月于北京

博客:http://blog.sina.com.cn/u/2940475465

磁能讲座(29)

《介绍一个简单实用的脉冲延时电路》

在磁能自由能的研究中,经常会碰到要使用各种可以改变脉冲的宽窄、位置等等的,方便可靠、简单实用的电路,下面就是一个你可能会用到的咚咚。

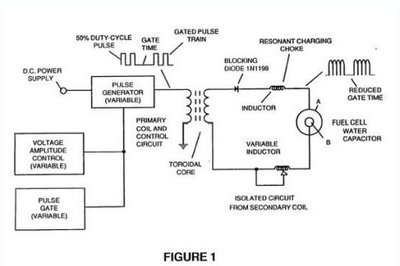

图一

先看图一中左面的电路(a),该电路由三个反相器,一个电容C,和一个电阻R组成。电路的延迟时间由RC的时间常数T决定:T=RC。R和C的值越大,脉冲的延迟时间越长。

右面的图波形(b)的含义是:

Ui是输入的脉冲信号,从电路(a)的左边进入。

UA是这个信号经过第一个反相器后在电路(a)中A点的波形,可以看到脉冲的相位已经被颠倒了,反相器之所以叫反相器,就是因为它可以把脉冲的相位颠倒过来。

UD是信号脉冲经过第二个反相器,和电容、电阻的迟滞作用后在电路(a)中D点形成的波形,可以看到脉冲已经明显变形了。

Uo是变形的波形经过第三个反相器后,在电路(a)的终端被整形、延迟后的脉冲波形。

(刘注:这个电路和磁能讲座(18)中介绍的CD4093的正边缘触发脉宽调整电路配合使用,可取得很好的效果,可相对一个基准脉冲,方便的移动脉冲的位置并调整脉冲的宽窄)

最后,如果需要,可以让被延迟并被反相的脉冲波形Uo,再经过一个反相器将相位重新正过来,以和输入波形的相位一致。

在具体的操作中,电路中使用的器件可以是6反相器CD4069,或类似的集成芯片,CD4069的引脚排列见下图。

图二 CD4069引脚图,该芯片中包含6个反相器

14 13 1211 109 8

1234567

图三是实物集成电路CD4069引脚排列顺序图

图四 是另一种不同封装形式的芯片,引脚排列顺序相同

图五 是反相器符号。

(注意,图一中的反相器的符号是长方形,也是左侧为输入,右侧有小圆圈标记的为输出)

所有此类集成电路芯片的引脚排列都和图三一样,印刷字体正面左下方第一个脚是脚1,而左上方第一个脚是芯片最后一个脚。

集成芯片CD4069的电压使用范围很宽,是3~15V,芯片的第14脚VDD是芯片电源正极,第7脚Vss是芯片电源负极。1、3、5、9、11、13引脚为6个独立的反相器的输入端,2、4、6、8、10、12引脚为6个反相器的输出端。下面是这个延迟电路的完整具体的接线图,属于老夫发明的一种速成傻瓜电路。

图六 具体接线图

图中Vin是信号输入端,Vout是信号输出端。电阻R可以是一个100K的可变电阻,电容C的容量要根据频率和需要选择(使用的频率越高,C的容量越小)。

注意,所有不使用的反相器的输入端(输出端不用管)都不能悬空,如图六所示,要接电源负极,也就是第7脚Vss。(说的清楚一些,在这个延迟电路中只需要使用3-4个反相器,而芯片中总共有6个反相器,剩下不用的反相器的输入端注意一定不能悬空,要可靠接地或接电源负极)

另外,如是cmos芯片,要注意防静电,如使用电烙铁直接焊接芯片,要使用带地线的烙铁,或关断电源再焊接。初学者最好使用带插座的芯片,焊好插座后,再将芯片插上。电路制作完成后,应在双踪示波器上调整波形,观察检测效果。

祝各位愉快!

刘中凯

2014年9月3日于北京

爱华网

爱华网