彩灯控制器设计

姓名:王瑞专业:通信工程

学号:0828401148指导老师:黄旭

目录

摘要…………………………………………3

1、系统设计要求………………………………3

2、系统总体结构………………………………3

3、功能模块 ……………………………………4

3.1时钟信号二分频模块 ……………………4

3.2计数器1模块…………………………4

3.3计数器2模块…………………………5

3.4循环右移模块…………………………6

3.5循环左移模块…………………………7

3.6循环取反模块…………………………8

3.7多选一模块 ……………………………9

3.8模块组合(系统)………………………10

4、系统调试 ……………………………………11

5、总结………………………………………11

彩灯控制器设计

摘要

一、系统设计要求

设计一个控制电路来实现8路彩灯按照一定的次序和时间间隔闪烁。具体要求如下:

1、当控制开关为0时,灯全灭;当控制开关为1时,从第一盏开始,依次点亮,时间间隔为1秒。期间一直保持只有一盏灯亮、其他灯全灭的状态。

2、8盏灯依次亮完后,从第8盏开始依次灭,期间一直保持只有一盏灯灭、其他灯全亮的状态。

3、当8盏灯依次灭完后,8盏灯同时亮同时灭,其时间间隔为0.5秒,并重复4次。

4、只要控制开关为1,上述亮灯次序不断重复。

5、用层次化设计方法设计该电路,编写各个功能模块的程序。

6、仿真各功能模块,通过观察有关波形确认电路设计是否正确。

7、完成电路设计后,用实验系统下载验证设计的正确性。

二、系统总体结构

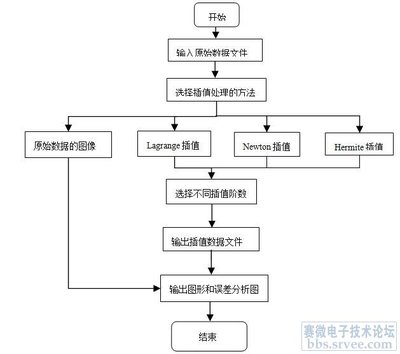

系统框图如下所示,

ENA为控制开关,输入信号为2Hz,经过分频器分频之后产生一个1Hz的时钟信号,用两个12位内部信号的左、右移后的中间8位来控制8个灯的亮与灭。计数器1和计数器2的作用:一方面用2Hz和1Hz的时钟信号控制灯亮、灭的时间间隔;另一方面控制八盏灯的依次亮、依次灭和全亮、全灭。

使能信号ENA为无效电平时(低电平),8只LED灯保持全灭的状态;当使能信号ENA为有效电平时(高电平),8只按照既定的花型进行变换,首先2Hz的时钟信号在分频器的左右下改变为1Hz的时钟信号,该1Hz的时钟信号送至计数器2、左移和右移模块,并由计数器2实现左、右移模块的选择。分别实现8只LED灯的自左向右依次点亮,以及自右向左依次熄灭的花型变换;当完成自右向左的花型变换后,计数器2给出一个控制信号给计数器1,执行全亮全灭的花型变换,该模块的时钟信号是未经分频器分频的原始时钟信号2Hz。只要使能信号有效,那么该系统就按照以上的花型变换顺序一直永序的变换下去。

三、各功能模块

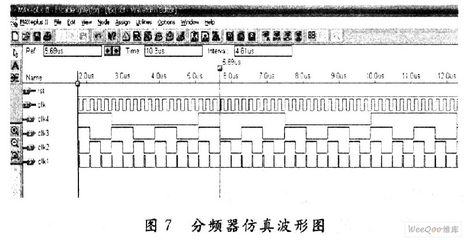

1、时钟信号二分频模块:

功能描述:该模块的功能主要是将频率为2Hz的时钟信号分频频率为1Hz的时钟信号,并将频率为1Hz的时钟信号输出给左移、右移模块作为这两个模块时钟触发信号。

代码部分:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY clk_div2 IS

PORT(CLK:IN STD_LOGIC;

OUTPUT:BUFFER STD_LOGIC);

END clk_div2 ;

ARCHITECTURE one OF clk_div2 IS

BEGIN

PROCESS(CLK)

BEGIN

IF CLK'EVENT AND CLK='1' THEN

OUTPUT<=NOT OUTPUT;

END IF;

ENDPROCESS;

END one;

仿真波形:

2、计数器模块:

功能描述:该模块的主要功能是通过计数,实现对左移及右移模块的选通,并在右移和左移模块完成后,跳转到循环取反模块执行指令。

计数器1代码部分:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY count1 IS

PORT(CLK,ENA:IN STD_LOGIC;

OUTPUT:BUFFER STD_LOGIC_VECTOR(1 DOWNTO 0));

END count1;

ARCHITECTURE one OF count1 IS

SIGNALCQ:STD_LOGIC_VECTOR(5 DOWNTO 0);

BEGIN

PROCESS(CLK,ENA)

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF ENA='1' THEN

IF CQ<"100111" THENCQ<=CQ+1;

IF CQ="100000" THEN OUTPUT<="10";

ELSIF CQ="100001" THEN OUTPUT<="01";

ELSIF CQ="100010" THEN OUTPUT<="10";

ELSIF CQ="100011" THEN OUTPUT<="01";

ELSIF CQ="100100" THEN OUTPUT<="10";

ELSIF CQ="100101" THEN OUTPUT<="01";

ELSIF CQ="100110" THEN OUTPUT<="10";

ELSIF CQ="100111" THEN OUTPUT<="01";

END IF;

ELSECQ<="000000";OUTPUT<="00";

END IF;

ELSE CQ<="111111";

END IF;

END IF;

END PROCESS;

END one;

仿真波形:

计数器2代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY count2 IS

PORT(CLK,ENA:IN STD_LOGIC;

OUTPUT:OUT STD_LOGIC_VECTOR(5 DOWNTO 0));

END count2;

ARCHITECTURE one OF count2 IS

SIGNALCQ:STD_LOGIC_VECTOR(5 DOWNTO 0);

BEGIN

PROCESS(CLK,ENA)

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF ENA='1' THEN

IF CQ<"010011" THENCQ<=CQ+1;

ELSE CQ<="000000";

END IF;

ELSE CQ<="111111";

END IF;

END IF;

END PROCESS;

OUTPUT<=CQ;

END one;

仿真波形:

3、循环右移模块:

功能描述:该功能实现8只LED灯的从左向右依次点亮的功能,点亮过程中,每时每刻都保证只有一个LED被点亮,其它LED全灭的状态。时间间隔为1S。

代码部分:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY rightmove IS

PORT(CLK,ENA:IN STD_LOGIC;

COUNT:IN STD_LOGIC_VECTOR(5 DOWNTO 0);

OUTPUT:OUT STD_LOGIC_VECTOR(11 DOWNTO 0));

END rightmove ;

ARCHITECTURE one OF rightmove IS

BEGIN

PROCESS(CLK,ENA,COUNT)

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IFENA='1' THEN

CASE COUNT IS

WHEN"000000"=>OUTPUT<="001000000000";

WHEN"000001"=>OUTPUT<="000100000000";

WHEN"000010"=>OUTPUT<="000010000000";

WHEN"000011"=>OUTPUT<="000001000000";

WHEN"000100"=>OUTPUT<="000000100000";

WHEN"000101"=>OUTPUT<="000000010000";

WHEN"000110"=>OUTPUT<="000000001000";

WHEN"000111"=>OUTPUT<="000000000100";

WHENOTHERS=>OUTPUT<="000000000000";

END CASE;

ELSE OUTPUT<="000000000000";

END IF;

END IF;

END PROCESS;

END one;

仿真波形:

4、循环左移模块:

功能描述:该功能实现8只LED灯在从左向右依次点亮结束后,从右向左依次熄灭一只LED,熄灭过程中,每时每刻都保证只有一个LED被熄灭,其它LED全亮的状态。时间间隔为1S。

代码部分:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY leftmove IS

PORT(CLK,ENA:IN STD_LOGIC;

COUNT:IN STD_LOGIC_VECTOR(5 DOWNTO 0);

OUTPUT:OUT STD_LOGIC_VECTOR(11 DOWNTO 0));

END leftmove ;

ARCHITECTURE one OF leftmove IS

BEGIN

PROCESS(CLK,ENA,COUNT)

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF ENA='1' THEN

CASE COUNT IS

WHEN"001000"=>OUTPUT<="111111111011";

WHEN"001001"=>OUTPUT<="111111110111";

WHEN"001010"=>OUTPUT<="111111101111";

WHEN"001011"=>OUTPUT<="111111011111";

WHEN"001100"=>OUTPUT<="111110111111";

WHEN"001101"=>OUTPUT<="111101111111";

WHEN"001110"=>OUTPUT<="111011111111";

WHEN"001111"=>OUTPUT<="110111111111";

WHENOTHERS=>OUTPUT<="000000000000";

END CASE;

ELSE OUTPUT<="000000000000";

END IF;

END IF;

END PROCESS;

END one;

仿真波形:

5、循环取反模块:

功能描述:该模块实现的是对完成逐个点亮和逐个熄灭的过程后,实现每秒2次的全亮、全灭的闪烁。即相邻两个动作之间的时间间隔为0.5S。

代码部分:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY qufan IS

PORT(CLK,ENA:IN STD_LOGIC;

COUNT:IN STD_LOGIC_VECTOR(1 DOWNTO 0);

OUTPUT:BUFFER STD_LOGIC_VECTOR(11 DOWNTO 0));

END qufan;

ARCHITECTURE one OF qufan IS

BEGIN

PROCESS(CLK,ENA,COUNT)

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF ENA='1' THEN

CASECOUNT IS

WHEN"10"=>OUTPUT<="111111111111";

WHEN "01"=>OUTPUT<=NOTOUTPUT;

WHENOTHERS=>OUTPUT<="000000000000";

END CASE;

ELSE OUTPUT<="000000000000";

END IF;

END IF;

END PROCESS;

END one;

仿真波形:

6、多选一模块:

功能描述:此模块选择左移、右移或者是循环取反中的一个模块信号送至8只LED灯。

代码部分:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY qufan IS

PORT(CLK,ENA:IN STD_LOGIC;

COUNT:IN STD_LOGIC_VECTOR(1 DOWNTO 0);

OUTPUT:BUFFER STD_LOGIC_VECTOR(11 DOWNTO 0));

END qufan;

ARCHITECTURE one OF qufan IS

BEGIN

PROCESS(CLK,ENA,COUNT)

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF ENA='1' THEN

CASE COUNT IS

WHEN"10"=>OUTPUT<="111111111111";

WHEN "01"=>OUTPUT<=NOTOUTPUT;

WHENOTHERS=>OUTPUT<="000000000000";

END CASE;

ELSE OUTPUT<="000000000000";

END IF;

END IF;

END PROCESS;

END one;

仿真波形:

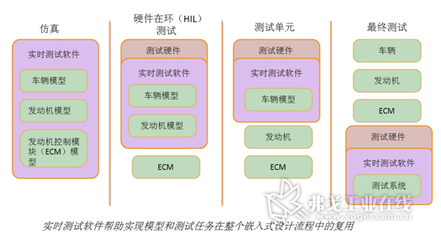

7、系统组合电路:

以上详细地介绍了各个模块的功能、代码以及仿真波形。下面将把6个分模块系统有序的整合在一起,形成一个功能完整的系统。

仿真波形:

四、系统调试

1、该系统使用开发板电路模式N0.6,其电路结构为

2、使用的可编程芯片型号为FLEX EPF10K10-PLCC84。

3、在将程序下载到实验箱上实际检测的时候,引脚的设置是一项简单

但极易出现错误的工作。时钟信号由clock0送出,其时钟频率为2Hz,

使能信号ENA接的是实验箱上的3号按键。

4、当控制开关ENA为0时,8只彩灯保持全灭的状态;当控制开关ENA

为1时,彩灯按照预先设定的先自左向右依次点亮,全部点亮后按照自右向左的顺序依次熄灭,依次渐亮和依次熄灭的过程中,始终保持只有一盏彩灯被点亮或熄灭,且时间间隔为1S。当彩灯依次熄灭后,加快变换频率,以0.5S的时间间隔全亮、全亮交替。

5、调试结果:此系统可以顺利的实现了4的设定显示效果。

五、总结

本次实验课题主要包括四个阶段:课题选择阶段、查阅资料阶段、编程仿真阶段、实验箱检测调试阶段。

课题的选定是抽签决定的,有不少人说彩灯是最简单的一个课题。不过我认为没什么简单困难之分,不同的只是你对待它的态度。

查阅资料阶段则主要围绕的是选择何种方案可以更好的实现要求得功能,并最终确定各个功能模块的实现方案。

编程仿真阶段则主要是把上一阶段确定的方案变为VHDL代码,并编译仿真得到仿真波形。

最后一个阶段就是实验箱检测和调试阶段,将已经编译仿真过的程序下载到实验箱进行实际的检测和调试。最终系统没出现什么问题,编译后的代码下载到实验箱后,彩灯顺利实现要求的花型变换。

最后要感谢老师的悉心指导,课程设计中,遇到了不少问题,多亏了老师的悉心指导才能够顺利、及时地解决问题,使得课题能够顺利完成。通过这次的课题设计,我深深体会到知识通过应用才能体现其价值。

爱华网

爱华网