时钟电路设计概述 - 数字电路设计 数字电子时钟电路图

时钟信号产生电路

先看图1中的两个时钟电路,不用我说,相信读者一眼就可以看得出来,左边的那个是有源晶振电路,右边的是无源晶振电路。

图1 两个时钟电路

振荡器就是可以产生一定频率的交变电流信号的电路

晶体振荡器,简称晶振,是利用了晶体的压电效应制造的,当在晶片的两面上加交变电压时,晶片会反复的机械变形而产生振动,而这种机械振动又会反过来产生交变电压。当外加交变电压的频率为某一特定值时,振幅明显加大,比其它频率下的振幅大得附加外部时钟电路,一般是一个放大反馈电路,只有一片晶振是不能实现震荡的多,产生共振,这种现象称为压电谐。

晶振相对于钟振而言其缺陷是信号质量较差,通常需要精确匹配外围电路(用于信号匹配的电容、电感、电阻等),更换不同频率的晶体时周边配置电路需要做相应的调整。

如果把完整的带晶体的振荡电路集成在一块,可能再加点其它控制功能集成到一起,封装好,引几个脚出来,这就是有源晶振,时钟振荡器,或简称钟振。英文叫Oscillator,而晶体则是Crystal。可以说Oscillator是Crystal经过深加工的产品,而Crystal是原材料。好多钟振一般还要做一些温度补偿电路在里面。让振荡频率能更加准确。

相对于无源晶体,有源晶振的缺陷是其信号电平是固定的,需要选择好合适输出电平,灵活性较差,而且价格高。

典型无源晶振电路

图2是典型的无源晶振电路。

图2 典型的无源晶振电路

与晶振并联的电阻的作用

与晶振并联的电阻R4是反馈电阻,是为了保证反相器输入端的工作点电压在VDD/2,这样在振荡信号反馈在输入端时,能保证反相器工作在适当的工作区。虽然去掉该电阻时,振荡电路仍工作了。但是如果从示波器看振荡波形就会不一致了,而且可能会造成振荡电路因工作点不合适而停振。所以千万不要省略此电阻。这个电阻是为了使本来为逻辑反相器的器件工作在线性区,以获得增益,在饱和区是没有增益的, 没有增益是无法振荡的。如果用芯片中的反相器来作振荡,必须外接这个电阻,对于CMOS而言可以是1M以上,对于TTL则比较复杂,视不同类型(S,LS…)而定。如果是芯片指定的晶振引脚,如在某些微处理器中,常常可以不加,因为芯片内部已经制作了,要仔细阅读DATA SHEET的有关说明。

与晶振串联的电阻的作用

和晶振的串联电阻(R3)常用来预防止晶振被过分驱动。晶振过分驱动的后果是将逐渐损耗减少晶振的接触电镀,这将引起频率的上升,并导致晶振早期失效。如何判断晶振是否被过分驱动? 电阻RS常用来防止晶振被过分驱动。过分驱动晶振会渐渐损耗减少晶振的接触电镀,这将引起频率的上升。可用一台示波器检测OSC输出脚,如果检测一非常清晰的正弦波,且正弦波的上限值和下限值都符合时钟输入需要,则晶振未被过分驱动;相反,如果正弦波形的波峰,波谷两端被削平,而使波形成为方形,则晶振被过分驱动。这时就需要用电阻RS来防止晶振被过分驱动。判断电阻RS值大小的最简单的方法就是串联一个5k或10k的微调电阻,从0开始慢慢调高,一直到正弦波不再被削平为止。通过此办法就可以找到最接近的电阻RS值。

晶振两个引脚两个电容的作用

这两个电容(C1,C2)叫晶振的负载电容,分别接在晶振的两个脚上和对地的电容,一般在几十皮法。它会影响到晶振的谐振频率和输出幅度,一般订购晶振时候供货方会问你负载电容是多少。

晶振的负载电容=[(Cd*Cg)/(Cd+Cg)]+Cic+△C式中Cd,Cg为分别接在晶振的两个脚上和对地的电容,Cic(集成电路内部电容)+△C(PCB上电容)经验值为3至5pf。

这两个电容串联的值是并联在谐振回路上的,会影响振荡频率。当两个电容量相等时,反馈系数是 0.5,一般是可以满足振荡条件的,但如果不易起振或振荡不稳定可以减小输入端对地电容量,而增加输出端的值以提高反馈量。

时钟缓冲器(Clock Buffer)

输出缓冲器的作用是加强时钟发生器的带负载能力,同时减少负载对时钟发生器的干扰和影响。时钟发生器可以选用芯片厂商的专用IC来实现,也可以采用分立元件进行设计。

图3是我公司在某款Wi-Fi产品的设计中采用的时钟缓冲电路。CY-2308是双边、通用零延迟缓存器,可用在需要严格输入-输出及输出-输出斜率的各种时钟分配应用中。

图3 时钟缓冲器CY-2308

图4是我公司在另外一款产品的开发中设计的分立元件时钟缓冲电路,其中的DNS意思为Design not Stuff。经实际产品检验,效果良好。

图4 分立元件时钟缓冲电路

时钟电路的EMC问题

对于任何数字信号,绝大部分能量都集中在转折频率以下,而转折频率与其数字边沿的上升和下降时间有关,而与其时钟速率无关。

滤波是最常用来降低信号波形的边缘速度的方法,也就是在信号路径中加上5到15pF的电容器,用以平缓信号的边缘速度。通常工程师会在电路设计中,靠近信号源头的位置,预留这些电容器的安装位置,到发生EMI问题时,再将电容器装置上去。若时钟电路采用串接式的终端电阻,滤波电容器装在电阻的两侧皆可,但为了获得最佳的信号终结与保持信号的完整性,滤波电容建议装在终端电阻之后靠信号来源的这一侧。

时钟电路的端接电阻

串行端接是通过在尽量靠近源端的位置串行插入一个电阻RS(典型10Ω到75Ω)到传输线中来实现的,如图5所示。串行端接是匹配信号源的阻抗,所插入的串行电阻阻值加上驱动源的输出阻抗应大于等于传输线阻抗(轻微过阻尼)。

图5 串行端接电阻

这种策略通过使源端反射系数为零从而抑制从负载反射回来的信号(负载端输入高阻,不吸收能量)再从源端反射回负载端。串行端接的优点在于:每条线只需要一个端接电阻,无需与电源相连接,消耗功率小。当驱动高容性负载时可提供限流作用,这种限流作用可以帮助减小地弹噪声。

多负载的端接

在实际电路中常常会遇到单一驱动源驱动多个负载的情况,这时需要根据负载情况及电路的布线拓扑结构来确定端接方式和使用端接的数量。一般情况下可以考虑以下两种方案。如果多个负载之间的距离较近,可通过一条传输线与驱动端连接,负载都位于这条传输线的终端,这时只需要一个端接电路。如采用串行端接,则在传输线源端加入一串行电阻即可,如图6所示。如采用并行端接(以简单并行端接为例),则端接应置于离源端距离最远的负载处,同时,线网的拓扑结构应优先采用菊花链的连接方式。

图6 多负载端接

如果多个负载之间的距离较远,需要通过多条传输线与驱动端连接,这时每个负载都需要一个端接电路。如采用串行端接,则在传输线源端每条传输线上均加入一串行电阻,如图a 所示。如采用并行端接(以简单并行端接为例),则应在每一负载处都进行端接,如图b 所示。

时钟电路设计笔记

设计时钟时需要注意什么问题?

时钟电路走线不能直接分叉,必要时要加时钟Buffer

还有呢?

PCB布线时不能拐直角

最好部在电源层和地层之间

到各个器件的距离最好差不多

时钟线应该尽量短,必要时可以用地线将时钟区圈起来

补充一点

要加始端串联匹配电阻

更多阅读

数字电子电路调心得一 ——时序电路的调试 数字电路心得

其实我应该先写模拟电子电路的心得,因为那是半年前就已结束的课程,自己也积累了颇多经验,不过由于鄙人的惰性,一直没写出来。然而,今天的一个电路实在是让我愤怒到一点脾气也没有了,所以才决意在这么繁忙的时刻写点东西。 本次设计是一个

如何区分电压串联负反馈电路和电流串联负反馈电路 电压串联负反馈电路图

负反馈放大电路从输出端的取样方式可以分为电压反馈和电流反馈从输入端的接入电路的方式可以分为串联反馈和并联反馈。最简单的区分方法是:若输出端的反馈取样点跟输出在同一点的话就是电压反馈,不在同一点的话就是电流反馈;在输入端,如

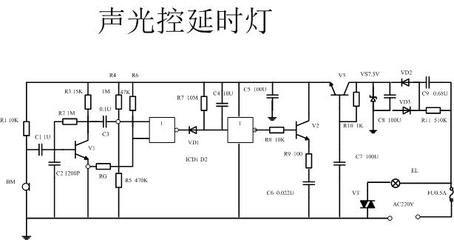

走廊灯延时开关电路 555延时开关电路图

用延时关灯的方式自动熄灭电灯。但笔者认为要想使这种开关得到推广使用,必须解决以下三个问题:1、便于安装,在不改变市电接线的条件下能与现有的照明开关互换、即要求电子节能开关是一个双端器件。2、要求电子节能开关关断时电阻无穷大

使用89C2051实现A/D的使用方法和程序A/D转换设计 at89c2051串口程序

一、选题的背景和意义:随着数字电子技术的迅速发展,用数字电路来处理模拟信号的情况更加普及。这就涉及到模拟信号与数字信号间的相互转换:从模拟信号到数字信号的转换称模/数转换(又称A/D转换),完成A/D转换的电路称A/D转换器(简称ADC);

电子电路基础知识- 电子电路基础

电子电路基础知识电路基础知识(一)电路基础知识(1)——电阻导电体对电流的阻碍作用称着电阻,用符号R表示,单位为欧姆、千欧、兆欧,分别用Ω、KΩ、MΩ表示。一、电阻的型号命名方法:国产电阻器的型号由四部分组成(不适用敏感电阻)第一部分:主

爱华网

爱华网