Contents

差分信号系统是采用双绞线进行信号传输的,双绞线中的一条信号线传送原信号,另一条传送的是与原信号反相的信号。差分信号是为了解决信号源和负载之间没有良好的参考地连接而采用的方法,它对电子产品的干扰起到固有的抑制作用。差分信号的另一个优点是它能减小信号线对外产生的电磁干扰(EMI)。差分对布线是一项要求在印刷电路板上创建利于差分信号(对等和反相的信号)平衡的传输系统的技术。差分线路一般与外部的差分信号系统相连接,如连接器或电缆。

需要注意的是在一对差分双绞线上耦合系数最好能大于90%,但在实际差分线路上一般耦合系数均小于50%。现在专家的意见是PCB布线的任务并不是使指定的差分阻抗能达到指标要求,而是使差分信号经过外部的电缆传送后到达目标器件仍能保持良好的信号质量。

著名的工业高速PCB设计专家LeeRitchey指出成功的差分信号线路设计并不要求达到指定的差分阻抗,而是要达到以下几点要求:

如需获得更多相关信息,可参阅Lee W. Ritchey的论文Differential Signaling Doesn'tRequire Differential Impedance,该论文可从http://www.speedingedge.com/RelatedArticles.htm上查阅。

在原理图中定义差分对

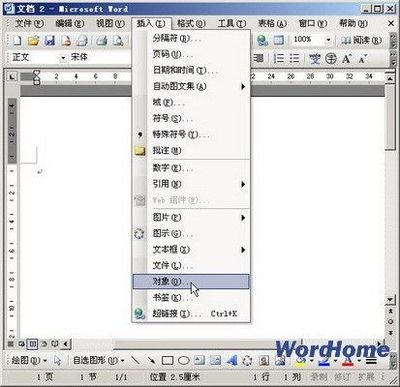

在菜单中Place>>Directive为差分网络放置差分对指令。差分对网络名称必须以“_N”和“_P”作为后辍。对差分网络放置指令后要对其参数进行配置,包括DifferentialPair名称以及True参数。

在设计同步的时候,差分对将从原理图转换到PCB中。

Place directives on the schematic to define differentialpairs.

在PCB中查看和管理差分对

在PCB面板的下拉列表中选择“Differential PairsEditor”后可以查看和管理已定义的差分对。图15-31所示的差分对属于全局的差分对类,当前V_RX0高亮显示,V_RX0_N和V_RX0_P组成差分对,“-”和“+”是系统的标志,指示了差分对的正负极性。

Differential pairs can be viewed and managed in theDifferential Pair Editor.

在PCB中定义差分对

用户不但可以在原理图中定义差分对,同样可以在PCB编辑器中定义差分对。

在PCB面板中选择Differential Pairs Editor模式并点击Add按钮。在弹出的DifferentialPair对话框中,在现有的网络中选择正极和负极网络,并对差分对进行命名后点击OK。

Quickly create pairs from the named nets.

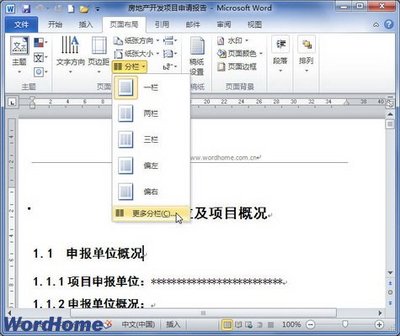

同样可以通过网络名称进行差分对的定义,对于一个差分对,其名称有相同的前辍,并以不同的后辍作区分,如TX0_P或TX0_N。在PCB面板中点击CreateFrom Nets按钮打开Create Differential Pairs FromNets对话框。在对话框顶部使用过滤器从现存的网络中筛选出差分对。如图所示为对电路板上以“_P”或“_N”结尾的网络名称进行筛选。

适用的设计规则

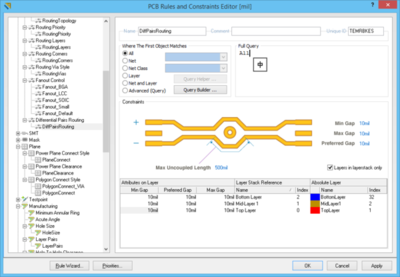

对差分对进行布线,必先在PCB Rules和ConstraintsEditor对话框(在Design>>Rules中调出)中的三项设计规则进行配置,分别是:

差分对线路的长度可以通过Interactive Diff Pair LengthTuning(在Tools菜单中)功能进行调整。该功能可以对差分对线路的期望长度和容限值进行实时调整,并具有不同的选项通过增加各种起伏的波纹状线路调节网络线路长度。

设置设计规则的辖域

设计规则的辖域定义了规则所作用的范围。差分对可以通过如下的检索条件例子对设计规则的辖域进行定义。

差分对布线

差分对布线是一对进行的,也就是对两个网络同时布线。对差分对进行布线,可从菜单中选取Place » DifferentialPair Routing或通过鼠标右键菜单调出差分对布线工具。此时将提示用户选取布线对象,点击差分对的任意一个网络开始布线。下图所示为差分对布线。

差分对布线中使用的是遇到第一个障碍停止或忽略障碍的交互式布线模式,使用SHIFT+R快捷键进行循环切换。差分对布线和交互式布线有部分相同的快捷键。使用数字小键盘中的*键进行换层。按5快捷键来循环可能的过孔模式。按Shift+F1快捷键来显示所有可能的快捷键。

Differential pairs are routed simultaneously.

包括管脚交换的FPGA设计中全面的差分对支持

现代的FPGA,即使在一些廉价的产品中也提供大量的管脚供用户配置成差分对。为了便于设计工作的开展,AltiumDesigner在FPGA和PCB设计中都对基于FPGA的差分对整合作全面的支持。

在FPGA设计中,可以把单一的网络定义到差分I/O上,如LVDS标准,这样软件就会把一对物理网络映射到PCB设计中。这个过程用户可以通过FPGASignal Manager进行控制。设计编译器同样可以确定管脚是否在PCB设计中用作差分对并正确映射到FPGA器件中。

差分对中对信号完整性的支持

AltiumDesigner的信号完整性分析提供对差分对仿真的全面支持。在FPGA管脚中使用LVDS标准能确保运用正确的信号完整性模型。

爱华网

爱华网