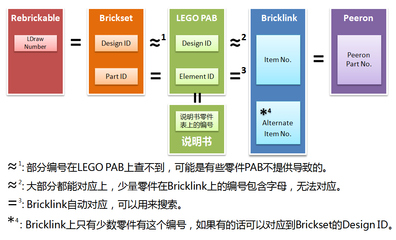

直奔主题吧,先来看看EP1C3T144的管脚图

我用红色箭头标示的就是EP1C3T144C8上所有跟CLK和PLL有关系的管脚,这是我从

Altea官方文档上面取出来的信息

BankNumber VREFBank PinName/Function OptionalFunction(s)T144

B1VREF0B1IOLVDS3p/CLKUSRpin 3

B1VREF2B1IODPCLK0pin 28

B1VREF0B1IODPCLK1pin10

B2VREF2B2IODPCLK2pin134

B2VREF0B2IODPCLK3pin119

B3VREF0B3IODPCLK4pin100

B3VREF2B3IODPCLK5pin82

B4VREF0B4IODPCLK6pin62

B4VREF2B4IODPCLK7pin47

VREF1B1VCCA_PLL1pin15

VREF1B1GNDA_PLL1pin18

VREF1B1GNDG_PLL1pin19

B1VREF1B1CLK0LVDSCLK1ppin16

B1VREF1B1CLK1LVDSCLK1npin17

B3VREF1B3CLK2LVDSCLK2ppin93

B3VREF1B3CLK3LVDSCLK2npin92

B1VREF1B1DCLKDCLKpin24

B1VREF1B1IOPLL1_OUTppin26

B1VREF1B1IOPLL1_OUTnpin27

注: LVDS:Low-Voltage Differential Signaling 低压差分信号

Pin Information for the Cyclone? EP1C3T144Device

下面是管脚的信息:

PinNamePin Type (1st, 2nd, &3rd Function)

CLKUSRI/O,Input

Pin Description

Optional user-supplied clock input. Synchronizesthe initialization of one or more devices. This pin can be used asa user I/O pin after configuration.

用户可选的时钟输入。同步一个或多个芯片的初始化(配置)。在配置完成后这个管脚可以当做普通的I/O口。

PinNamePin Type (1st, 2nd, &3rd Function)

DPCLK[7..0]I/O

Pin Description

Dual-purpose clock pins that can connect to theglobal clock network. These pins can be used for high fan-outcontrol signals, such as clocks, clears, IRDY, TRDY, or DQSsignals. These pins are also available as user I/O pins.

2种功能的时钟管脚,这些管脚都被连接到全局时钟网络。既可以用于高扇出的控制信号,如时钟,清零,IRDY, TRDY, orDQS等信号,还可以当做普通的I/O口。

PinNamePin Type (1st, 2nd, &3rd Function)

VCCA_PLL[1..2]Power

Pin Description

Analog power for PLLs[1..2]. The designer mustconnect this pin to 1.5 V, even if the PLL is not used.

锁相环的模拟电源。此管脚必须连接到1.5V的模拟电压,即使锁相环没有用到。

PinNamePin Type (1st, 2nd, &3rd Function)

GNDA_PLL[1..2]Ground

Pin Description

Analog ground for PLLs[1..2]. The designer canconnect this pin to the GND plane on the board.

锁相环的模拟地。此管脚可以连接到板子上的地层。

PinNamePin Type (1st, 2nd, &3rd Function)

GNDG_PLL[1..2]Ground

Pin Description

Guard ring ground for PLLs[1..2]. The designer canconnect this pin to the GND plane on the board.

锁相环的防护环式地层,此管脚可以连接到板子上的地层。(这个涉及到IC设计的专业知识,我也不清楚 防护环式地层 是什么意思)。

PinNamePin Type (1st, 2nd, &3rd Function)

CLK0Input, LVDS Input

Pin Description

Dedicated global clock input. The dual-function ofCLK0 is LVDSCLK1p, which is used for differential input toPLL1.

专用的全局输入时钟。这个管脚还有个功能就是当做LVDSCLK1p,即给PLL输入不同频率的时钟。

LVDSCLK1p :Dual-purpose LVDS clock input toPLL1. If differential input to PLL1 is notrequired, this pin is available as the CLK0 input pin

LVDSCLK1p:第二个功能就是当做PLL的时钟输入,如果PLL不需要不同频率的时钟输入的话,这个管脚就是全局输入时钟。

这个功能一般我们用不到,在Altera的文档中也有介绍,

Manual Clock Switchover

The Cyclone II PLLssupport manual switchover of the reference clock through internallogic. This enables you to switch between two reference inputclocks.

Cyclone II器件中的PLL支持通过内部的逻辑来控制切换 PLL1的输入参考时钟,这样你可以在2个输入时钟中切换,仔细的朋友可能看到过。

PinNamePin Type (1st, 2nd, &3rd Function)

CLK1Input,LVDS Input

Pin Description

Dedicated global clock input. The dual-function ofCLK1 is LVDSCLK1n, which is used fordifferential input to PLL1. The EP1C3T100 does not support this clock pin.

专用的全局输入时钟。这个管脚还有个功能就是当做LVDSCLK1n,即给PLL1输入不同频率的时钟,但是

EP1C3T100芯片不支持这个时钟输入

PinNamePin Type (1st, 2nd, &3rd Function)

CLK2Input, LVDS Input

Pin Description

Dedicated global clock input. The dual-function ofCLK2 is LVDSCLK2p, which is used for differential input toPLL2.

专用的全局输入时钟。这个管脚还有个功能就是当做LVDSCLK2p,即给PLL2输入不同频率的时钟。

PinNamePin Type (1st, 2nd, &3rd Function)

CLK3Input, LVDS Input

PinDescription

Dedicated global clock input. The dual-function ofCLK3 is LVDSCLK2n, which is used for differential input to PLL2.The EP1C3T100 does not support this clock pin.

专用的全局输入时钟。这个管脚还有个功能就是当做LVDSCLK2p,即给PLL2输入不同频率的时钟,但是

EP1C3T100芯片不支持这个时钟输入。

Pin NamePinType (1st, 2nd, &3rd Function)

DCLKInput (PS mode), Output (AS mode)

Pin Description

In passive serial configuration mode, DCLK is aclock input used to clock configuration data from an externalsource into the Cyclone device. In active serial configurationmode, DCLK is a clock output from the Cyclone device (the Cyclonedevice acts as master in this mode). This is a dedicated pin usedfor configuration.

在PS配置模式下,DCLK是用于将.sof文件数据下载到芯片内部sram里面的时钟,对FPGA芯片来说是输入时钟(控制下载速度),在AS配置模式下,DCLK是FPGA的输出时钟(也是控制下载速度),用于将.pof文件数据下载到外部串行配置芯片EPCS中。

PinNamePin Type (1st, 2nd, &3rd Function)

PLL1_OUTpI/O, Output

Pin Description

External clock output from PLL 1. This pin can beused with differential or single ended I/O standards. If clockoutput from PLL1 is not used, this pin is available as a user I/Opin. The EP1C3T100 does not support this output pin.

PLL1输出给外部器件(如SDRAM)用的时钟,输出的时钟可以是差分或单端I/O标准。如果实例化PLL时,没有用到此时钟,这个管脚也可以当做普通的I/O口,EP1C3T100芯片不支持这个时钟输出

PinNamePin Type (1st, 2nd, &3rd Function)

PLL1_OUTnI/O,Output

Pin Description

Negative terminal forexternal clock output from PLL1. If the clock output is singleended, this pin is available as a user I/O pin. The EP1C3T100 doesnot support this output pin.

PLL1输出给外部器件(如SDRAM)用的时钟的负端。如果输出时钟是单端信号,这个管脚也可以当做普通的I/O口。

分析完了,在来看看代码,声明有些复位处理是学习特权同学的方法。

module pll_100M (

clk,rst_n,

sys_rst_n,sdram_clk

);

input clk;//FPAG输入时钟信号20MHz

inputrst_n; //FPGA输入复位信号

outputsys_rst_n;//系统复位信号,低有效

outputsdram_clk;//PLL输出100MHz时钟,送给外部SDRAM

wirelocked;//PLL输出有效标志位,高表示PLL输出有效

wireclk_100M;//PLL输出100MHz时钟,内部用

//----------------------------------------------

//PLL复位信号产生,高有效

//异步复位,同步释放

wirepll_rst;//PLL复位信号,高有效

reg rst_reg1,rst_reg2;

always @(posedge clk or negedge rst_n)

if(!rst_n)

rst_reg1 <= 1'b1;

else

rst_reg1 <= 1'b0;

always @(posedge clk or negedge rst_n)

if(!rst_n)

rst_reg2 <= 1'b1;

else

rst_reg2 <= rst_reg1;

assign pll_rst = rst_reg2;

//----------------------------------------------

//----------------------------------------------

//系统复位信号产生,低有效

//异步复位,同步释放

wire sys_rst_n; //系统复位信号,低有效

wire sysrst_nr0;

reg sysrst_nr1,sysrst_nr2;

assign sysrst_nr0 = rst_n &locked; //系统复位直到PLL有效输出

always @(posedge clk_100M or negedgesysrst_nr0)

if(!sysrst_nr0) sysrst_nr1 <= 1'b0;

else sysrst_nr1 <= 1'b1;

always @(posedge clk_100M or negedgesysrst_nr0)

if(!sysrst_nr0) sysrst_nr2 <= 1'b0;

else sysrst_nr2 <= sysrst_nr1;

assign sys_rst_n = sysrst_nr2;

//----------------------------------------------

//----------------------------------------------

//例化PLL产生模块

pll_ctrlU1(

.areset(pll_rst), //PLL复位信号,高电平复位

.inclk0(clk),//PLL输入时钟,20MHz

.c0(clk_100M),//PLL输出100MHz时钟

.e0(sdram_clk),//PLL输出100MHz时钟,送给外部SDRAM

.locked(locked)//PLL输出有效标志位,高表示PLL输出有效

);

endmodule

如果分配管脚时,将sdram_clk分配到pin 28 (DPCLK0),走到布局布线时就会报错:

右键 点击 HELP,我非常推荐大家在用Quartus时,遇到错误到HELP里面去找答案,这是最有效的解决方法。

Can't place<name> PLL"<name>" because I/O pin"<name>" (port type<name> of the PLL) is assignedto a location which is not connected to port type<name> of any PLL on thedevice

CAUSE: You assigned a pin to a location that isnot connected to the specified port type of the specified fast PLLor enhanced PLL. The Fitter cannot place the PLL.

ACTION: Change the location assignment for theI/O pin or delete the assignment.

就是在分配管脚时,DPCLK这样的管脚不支持 输出高频的时钟,解决方法:重新分配适合的管脚。

如果分配管脚时,将sdram_clk分配到pin 16(CLK0),就不可以,因为CLK0~CLK3是输入时钟管脚。

如果分配管脚时,将sdram_clk分配到pin 26 (PLL1_OUTp),编译通过

如果分配管脚时,将sdram_clk分配到 pin 27(PLL1_OUTn),走到布局布线时还是会报错:

Can't place<name> PLL"<name>" in target device dueto device constraints

CAUSE: You selected a target device for thecurrent project. However, the Fitter cannot place the specifiedfast PLL or enhanced PLL in the target device due to deviceconstraints.

ACTION: Locate the source of the message todetermine the nature of the error. Modify the design accordingly sothat the Fitter can place the PLL. Click the + icon to expand thismessage in the Messages window or Messages section of the Reportwindow to display details about why the Quartus II software did notplace the PLL.

原因是器件不支持。

全文完。总结了这么多,嘿嘿,其实实验室板子上有一块SDRAM,当时学习了SDRAM好一段时间,最后上板子调试的时候分配sdram_clk管脚时,不能通过,当时也没有搞清楚为什么,现在清楚了。以后画板子的时候这点也需要注意下,为画板子打好基础吧,到时就当毕业设计咯。

文中有那里错误的地方欢迎大家指正,一起学习。翻译也可能有错误的地方,像这样的东西还是推荐大家看Altera官方原汁原味的文档,可以参考下我的分析。附件中有工程代码和EP1C3T144C8的管脚信息文档。

爱华网

爱华网