begin。。。end之间是顺序执行的,但是你这里又是非阻塞赋值,又是for语句,就比较复杂了。不过还是可以分析出来。首先非阻塞赋值是在这个模块结束的时候一起完成赋值的。并不是下一个下降沿才执行,这个模块最后一条语句就是赋值语句,所以基本上是立即执行了(阻塞赋值是立即执行的,如果有多个赋值,就会阻碍下一条赋值语句)。其次,for语句在这里,其实是一个时钟只执行一次,就是说第一个下降沿q[2]<=q[1],第二个下降沿q[3]<=q[2],这样理解下来,其实begin。。。end之间只有一条语句,也就没有什么顺序不顺序,先后次序的事情了

说了这么多,看一下运行结果就清楚了,把你的代码小小的修改了一下如下:

moduleeeee(clk,a,q);

inputclk;

inputa;

output[6:0]q;

reg[6:0]q;

reg[2:0]p;

always@(negedgeclk)begin

q[1]<=a;

for(p=1;p<6;p=p+1)

q[p+1]<=q[p];

end

endmodule

向左转|向右转for循环在一个时钟下降沿时执行六次的,你给的程序中只赋了一个值看不出来,我对你的代码又加了一个非阻塞。

module eeee (clk,a,q);

input clk;

input a;

output[6:0]q;

reg [6:0]q;

reg [2:0]p;

always @(negedge clk) begin

q[1] <= a;

for(p=1;p<6;p=p+1)

q[p+1]<=q[p];

q[3]<=a;

end

endmodule

什么叫顺序语句呢?是一条语句执行完才执行下一条吗?加入非阻塞是不是那些加入的非阻塞按并行处理

- 回答

顺序语句是执行完一句再执行下一句,如果有非阻塞就要按照并行处理,再说几个概念:

并行,顺序:verilog主要的模块之间都是并行执行的,例如各个always之间 如果你在一个always中要对a赋值,而在另一个always中要使用a的值,这时候就要注意了,两者并行的,处理先后不能确定。 你当前处理的a,是这个时钟被赋值的还是上一时钟被赋值的,意义可能完全不同,这就是并行需要考虑的问题。

而在always内部,一般使用了begin...end。这里面的内容都是顺序执行的,比如b=a; c=b,先执行一条,再执行下一条,那就是c=a了 如果里面有两组if/else,就是先执行前一组,再执行后一组。但是如果是非阻塞,那就要特殊对待,多个非阻塞赋值是在一个块结束时一起执行的,比如b<=a; c<=b,那就跟之前不同了,当执行c<=b 时b还没有变化成a的值,因此 这个赋值的结果是b被赋值前的值,这两条语句其实是独立的、并行的。好处是放得先后顺序没关系,只要在一个块内,随便写。这个不是很好理解,怎么说了begin...end之间是顺序,到了非阻塞就又变成并行执行的呢。 不好理解也没办法, verilog就是这样,先告诉你是这样的,然后又告诉你这样行不通,习惯就好了,另外掌握几条原则:组合逻辑用阻塞赋值,时序逻辑用非阻塞赋值,同一个模块中不要既用阻塞又用非阻塞...

掌握一条思路:verilog是硬件,是电路。所以调试的时候不能设置断点 所以所有模块都是并行,毕竟一上电整个板子都有电了,你不能说让它没电就没电,但是你可以在代码中加个控制,让它到了特定时候才干活。

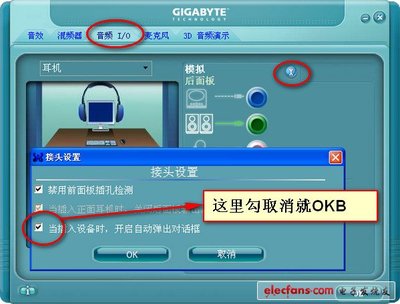

再说这个程序,不知道你能不能看到上面的图片,for循环是分了6个时钟才执行完的(我之前也以为是一个下降沿就执行完了 是仿真过才知道不是)。我设置了输入a,除了第一个时钟为1,之后都为0,利用这个1给最低位赋值,可以看出程序运行的顺序,对着图片看看吧。另外,for循环在硬件中效率很低,尽量少用,还是越简单越明确越好

爱华网

爱华网