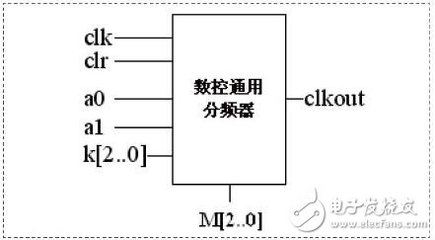

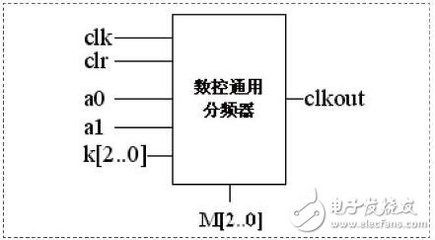

在FPGA中进行电路设计时,为了得到与输入时钟不同的频率,我们的一般做法是用FPGA自带的PLL或DCM实现,这在Altera和Xilinx中是一样的。但是,如果对时钟的性能要求不高,我们也可以自己用语言实现简单的分频电路,这样就只消耗了少量的资源而实现了时钟的分频要求,我们把这种设计叫做分频器设计。

分频器分为两种:偶分频和奇分频。对于偶分频电路,其实现较简单,一般做法是通过计数器计数,达到计数值上限(上限值为N/2-1,N为分频数目)后输出时钟取反同时计数器归零。以10分频电路为例,。其仿真结果如下图所示:

如上图所示,clk为输入时钟,cnt为计数器,clk_div为输出时钟,可以看出clk_div为clk的10分频时钟。

对于奇数分频器,有两种类型:一种是占空比不限定的,另一种为占空比为50%的。对于占空比不限定的奇数分频器,一般将计数器的上限值为N-1,当计数值到(N-1)/2时,输出时钟取反,当计数器达到上限值N-1时,输出时钟再取反同时计数器归零。以5分频为例,其仿真结果如下图所示:

如上图所示,clk为输入时钟,cnt为计数器,clk_div为输出时钟,可以看出clk_div为clk的5分频时钟,其占空比为40%。

对于占空比为50%的奇分频器,其电路设计相对复杂些。我们需要分别去采输入时钟的上升沿和下降沿分别计数,然后得到两个占空比不为50%的分频时钟(方法同占空比不限定的奇分频器),再将两个时钟相或便可得到占空比为50%的分频时钟。同样以5分频为例,其仿真结果如下图所示:

如上图所示,clk为输入时钟,cnt_pos为上升沿计数器,cnt_neg为下降沿计数器,clk_div为输出时钟,可以看出clk_div为clk的5分频时钟,其占空比为50%。

以上介绍了偶分频计数器、占空比不限定的奇分频计数器和占空比为50%的奇分频计数器,对于一般的分频器需求来讲,这有三种分频器电路已经够用。

爱华网

爱华网